[반도체 소자] MOS 구조의 에너지 밴드 다이어그램

지난 포스팅에서 간략하게 알아보았던 MOS 구조에 대해서 조금더 자세하게 살펴보도록 하겠습니다.

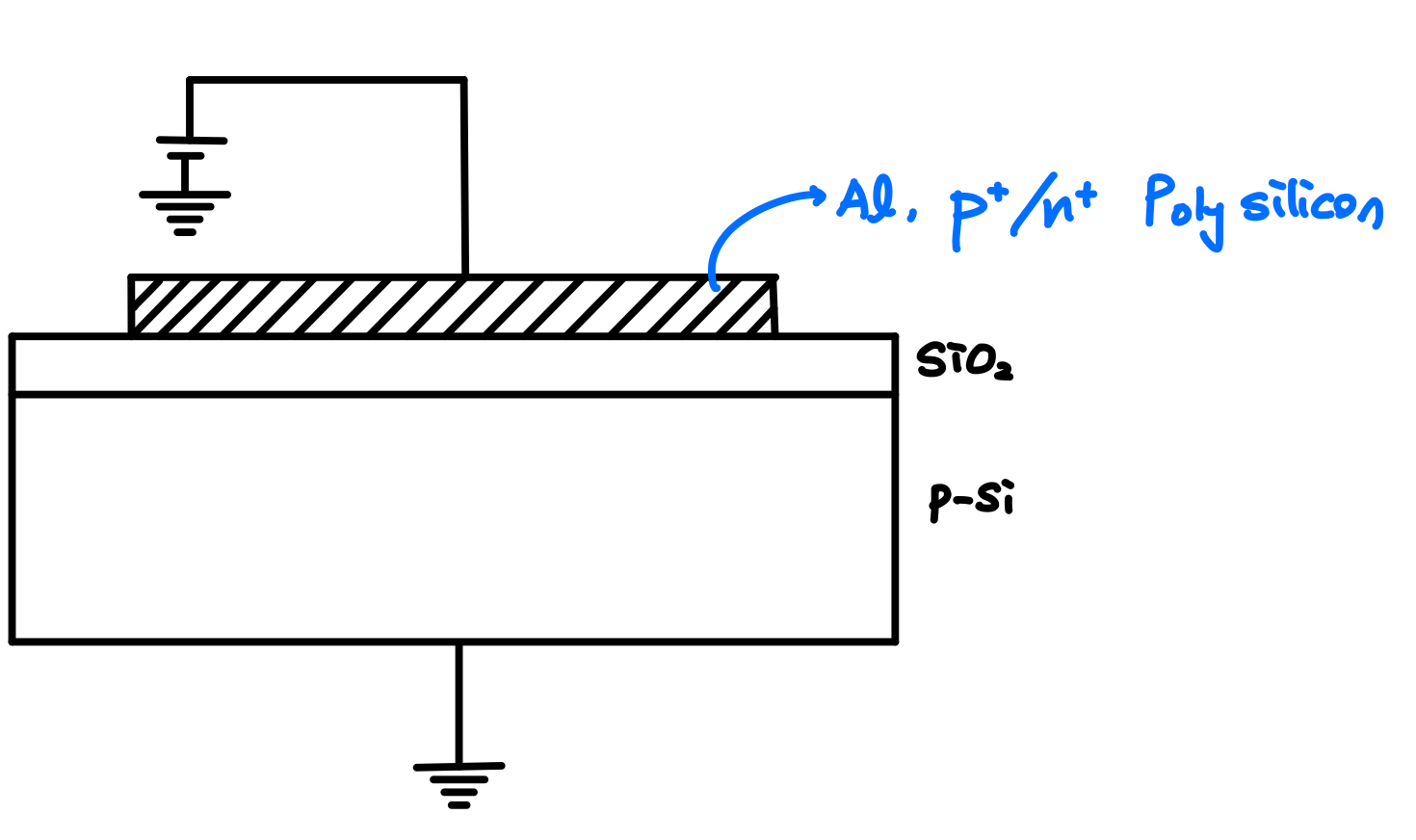

MOSCAP의 구조를 다시 살펴봅시다.

Semiconductor 위에 절연막이 올라가고 그 위에 Metal Gate가 올라가는 구조를 MOS(Metal Oxide Semiconductor) 구조라고 했었죠.

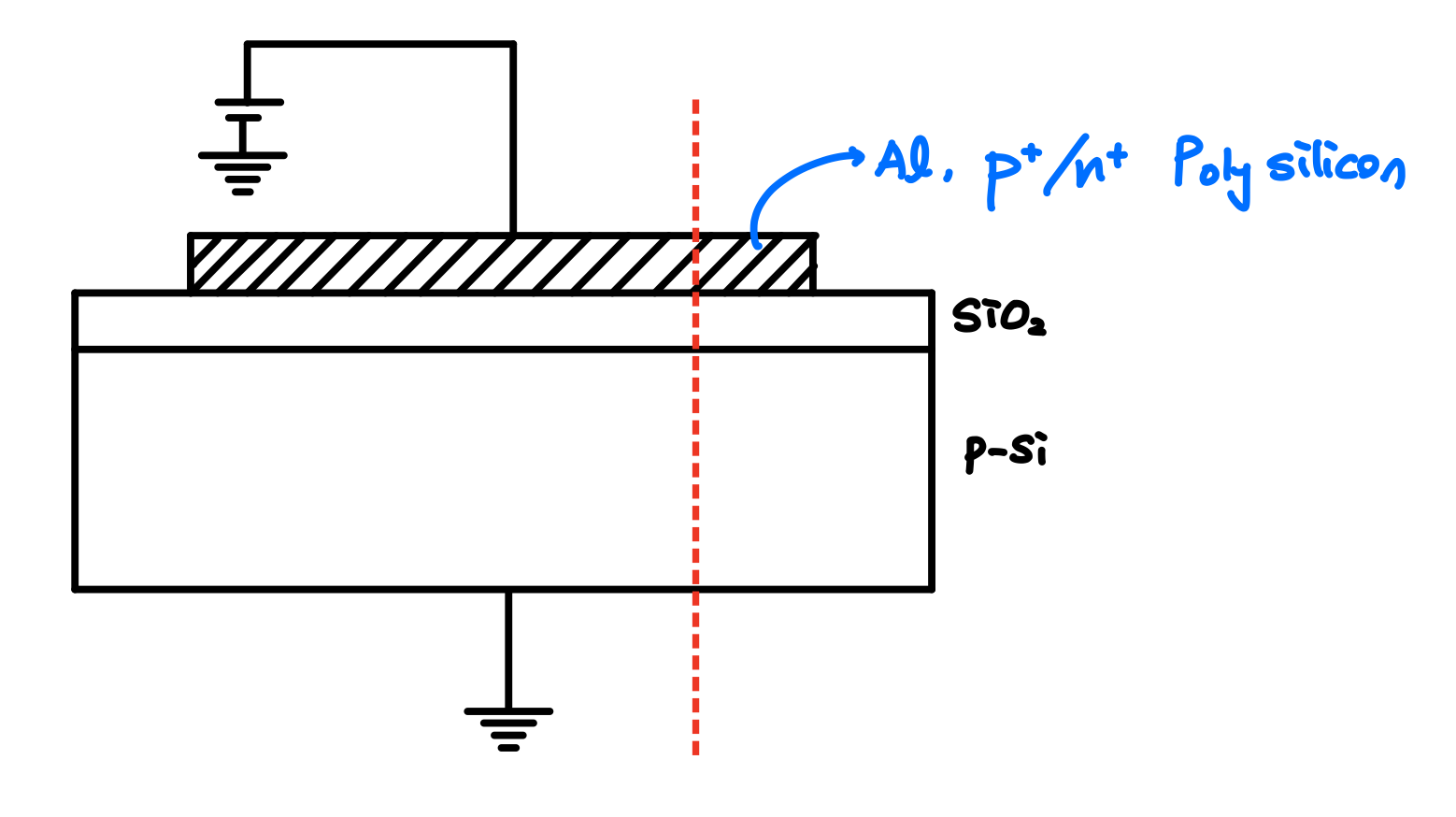

이번 포스팅 에서는 이러한 MOS 구조에 대해 에너지 밴드 다이어그램을 그려보겠습니다. 단면은 아래 그림과 같이 잘라낸 단면입니다.

Energy Band Diagram before Contact

먼저 각 층이 접합되지 않았다고 가정하고 단면의 에너지 밴드 다이어그램을 그려봅시다.

위의 그림처럼 잘라보면 제일먼저 Metal 그 다음에 Oxide, Silicon 순으로 지나가게 돠고, 아래와 같이 에너지밴드 다이어 그램이 그려집니다.

Metal은 Fermi Level까지 전자가 가득 차있었죠. Metal의 Fermi Level이 있고 그리고 그 위에 기준이 되는 Vacuum level이 있죠. 그래서 Fermi Level에 있는 전자를 Vaccum level까지 떼어낼 때 해야 하는 일을 일함수라고 합니다. 알루미늄의 경우에는 일함수가 4.21eV입니다.

이제 Metal을 지나가면 SiO2를 만나게 되겠죠. SiO2의 경우에는 Metal이 아니기 때문에 Conduction Band Edge와 Valence Band Edge가 존재하게 되겠죠. 각각의 위치는 그림에 표시한 Ec, Ev가 될겁니다. 그리고 이 사이의 간격 즉, Band Gap이 8eV정도로 굉장히 넓어요. 그리고 Conduction Band Edge와 Vacuum 사이의 에너지 차이를 Electron Affinity(전자 친화도)라고 합니다. 화학 분야에서 원소별 Electron Affinity 값을 측정해서 테이블로 만들어 놓았습니다. 우리는 이것을 가져다 쓰기만 하면 됩니다. SiO2의 경우는 Electron Affinity가 0.95eV라고 알려져 있습니다.

마지막으로 Silicon입니다. Si의 경우에도 SiO2와 마찬가지로 Conduction Band Edge와 Valence Band Edge가 존재합니다. 이 때 Si의 Electron Affinity는 4.15eV입니다. Si의 Band Gap은 1.12eV 정도였죠. 그래서 Conduction Band Egde에서 1.12eV정도 아래에 Valence Band Edge가 존재함을 볼 수 있습니다. Band Gap은 물질의 종류에 따라 달라지는 값이었죠.

여기서 짚고 넘어가야 할 것이 우리가 사용했던 Si는 p type Si이었죠. p type Si는 Fermi Level이 밴드 갭의 중앙인 intrinsic level 보다 아래에 형성됩니다. 이것을 EFS라고 합니다. EFS와 Ev사이에 에너지 차이가 0.27eV인 건 왜 그럴까요? 이건 그냥 반도체를 만드는 사람이 Si에 Donor의 도핑을 얼마나 해주냐에 따라 결정되는 값입니다. 위의 그림에선 그냥 예시를 든 것이라고 생각해도 됩니다.

이 때 Dopant의 농도는 다음과 같은 식을 사용하여 구할 수 있었습니다.

$ P_0 = N_v e^{(E_v - E_F) \over kT} $

$ N_v = 1.04 * 10^{19} cm^{-3}$

$ N_A = 3 * 10^{15} cm^{-3} $

$P_0$가 Dopant의 농도이니까 $P_0$에 따라 $E_v - E_F$ 가 변하는 것을 알 수 있습니다. 그래서 $E_{FS}$와 $E_v$ 사이의 간격은 Doping Concentration에 의해 결정된다는 것을 알 수 있습니다. 이 간격은 도핑을 많이 하면 $E_{FS}$와 $E_v$ 사이의 간격이 멀어지고 조금하면 가까워지게 될 것입니다.

여기서 알아야할 것이 Metal의 Fermi Level 그리고 SiO2의 Conduction Band Edge 사이의 간격을 Schottky Barrier Height Between Al and SiO2라고 합니다.또한 SiO2의 Conduction Band Edge와 Si의 Conduction Band Edge 사이의 간격을 Schottky Barrier Height Between SiO2 and Si라고 합니다. 이것을 다시 그림에 나타내보면 아래의 그림과 같이 될 것입니다.

이 Schottky Barrier Height는 물질에 따라 변하는 특성입니다.

지금까지 본 에너지 밴드 다이어그램은 Al, SiO2, Si가 모두 떨어져있을 때를 그린 것입니다. 이제부터 만약 이 세 물질을 붙인다면 어떤 Diagram이 될 것인가를 보도록 하겠습니다.

Energy Band Diagram in Thermal Equilibrium

이 세가지 물질을 접합시켰을 때, 에너지 밴드 다이어그램을 Thermal Equilibrium에서의 에너지 밴드 다이어그램이라고 합니다. Thermal Equilibrium이 무엇인지는 이전에 다이오드를 살펴볼 때 얘기했죠? MOS 구조에 에너지를 주지도 구조로부터 에너지를 받지도 않는 상태를 Thermal Equilibrium 상태라고 했습니다. 즉 쉽게 말해서 전기에너지나 빛에너지를 주지 않는 것이죠.

아무것도 하지 않은 상태 즉, Thermal Equilibrium 상태에서 MOS 구조의 단면에서 에너지 밴드 다이어그램이 어떻게 될 지 살펴봅시다.

Postulate

이 때 에너지 밴드 다이어그램을 그리기 위해 두 가지 가정이 필요하며, 각 가정은 다음과 같습니다.

1. Si - SiO2 - Metal 구조를 만들었을 때, Schottky Barrier Height는 그대로 유지된다.

각 층끼리 반응해서 새로운 물질이 만들어지는게 아니라 그냥 접합을 할 뿐이기 때문에 각 물질간의 Schottky Barrier Height는 유지가 된다고 가정하는 것은 타당합니다.

2. Fermi Level의 Gradient는 0이다. (즉, ${dE_F \over dx }= 0$)

반도체 소자가 Thermal Equilibrium에 있다는 것은 Fermi Level의 x에 대한 미분값이 0이 되었던 것 기억 나시나요? 따라서 Fermi Level이 소자 전체에 대해서 일정하다고 가정하는 것은 타당합니다.

Energy Band Diagram

이제 위의 가정에 기반하여 그림을 한번 그려보겠습니다.

가정에 의해서 MOS 구조 전체의 Fermi Level이 일정하고, 각 층간 Schottky Barrier Height가 3.26eV, 3.2eV로 일정할 것입니다. 또한 각 층을 접합한다고 해서 p type Si의 도핑 농도는 일정합니다. 따라서 MOS의 Fermi Level을 기준으로 $E_v$는 0.27eV 아래 $E_c$는 0.85eV위에 존재할 것입니다. 하지만 이 때, Metal과 Si의 Fermi Level을 맞추기 위해 Si의 Fermi Level을 올려주어야 합니다. Si의 Fermi level이 올라오면 Si의 Conduction Band Edge와 Valence Band Edge가 모두 올라가게 되겠죠? 그러면서 SiO2와 Si의 접합하는 부분이 휘게 됩니다.

이것을 토대로 그림을 그려보면 다음과 같이 그려집니다.

이 때, Si의 에너지 밴드가 굽지 않고 일정한 부분을 Bulk라고 부릅니다. Bulk 부분은 Si의 에너지 밴드 모양을 그대로 유지하지만 SiO2와 Si가 만나는 계면은 에너지 밴드가 구부러지게 됩니다. 이렇게 구부러지면서 Intrinsic level 또한 같이 구부러지는 현상이 발생하게 됩니다.

가운데는 SiO2가 위치하는 자리인데요. 이곳을 주목해서 보아야 합니다. 각 계면의 Schottky Barrier Height를 맞춰주려다 보니 SiO2의 내부에서 에너지 레벨의 차이가 생기게 되죠. 이것은 SiO2 내부에 포텐셜 차이가 생긴다는 이야기죠.

주목해야 할 부분이 한 가지 더 있습니다. 이 그림에서 Oxide와 Si가 만나는 부분을 보시면 $E_v$와 $E_{FS}$의 차이가 Bulk 부분에 비해 넓어진다는 것을 알 수 있는데요. 이 때 Bulk 에서의 정공의 농도를 $P_0$라고 하고, 계면에서의 정공의 농도를 $P_s$하고 하면, Fermi Level과 Valence Band Edge 사이의 간격이 넓어진다는 것은 $P_s$가 $P_0$보다 작다는 것을 의미하는 것이죠. 따라서 이 계면에서의 상태는 Majority Carrier의 농도가 줄었기 때문에 Depletion 상태라고 볼 수 있는 것입니다. 그리고 이 부분을 Depletion Region이라고 말합니다.

반면 Bulk 부분은 Depletion Region과 대조되는 의미로 Neutral Region이라고 부르기도 합니다.

※ 제가 개인적으로 공부한 내용을 요약해서 올리는 블로그입니다. 틀린 점이 있을 수 있습니다.

※ 질문 환영합니다. 댓글로 남겨주세요.

'전자공학 > 반도체공학' 카테고리의 다른 글

| [반도체소자] MOS Threshold Voltage (0) | 2021.03.07 |

|---|---|

| [반도체소자] MOS Surface Potential (0) | 2021.03.07 |

| [반도체 소자] MOS 구조의 Electric Field (0) | 2021.03.06 |

| [반도체소자] MOS 계면 상태 (1) | 2021.03.04 |

| [반도체소자] MOSCAP, MOSFET 개요 (0) | 2021.02.27 |